* Question

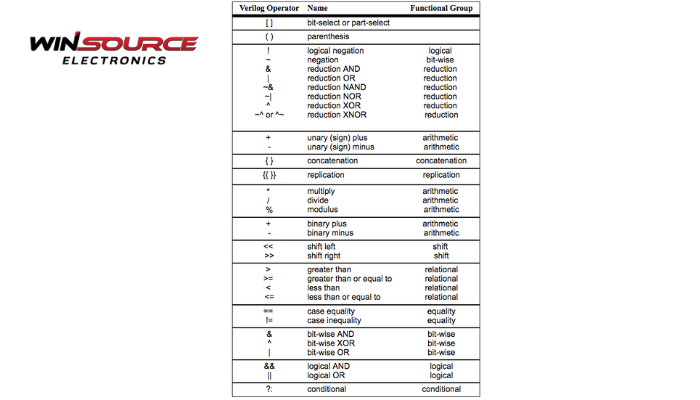

Verilog HDL provides a rich set of operators, which can be divided into different types according to the computing function.

* Answer

In Verilog HDL (Hardware Description Language), operators are used to perform computations and manipulate data. These operators are categorized based on their computing functions as follows:

1. Arithmetic Operators

– Purpose: Perform mathematical operations.

– Examples:

– `+` (Addition)

– `-` (Subtraction)

– “ (Multiplication)

– `/` (Division)

– `%` (Modulus)

2. Relational Operators

– Purpose: Compare values and return a Boolean result (True or False).

– Examples:

– `>` (Greater than)

– `<` (Less than)

– `>=` (Greater than or equal to)

– `<=` (Less than or equal to)

3. Equality Operators

– Purpose: Compare equality of operands.

– Examples:

– `==` (Logical equality)

– `!=` (Logical inequality)

– `===` (Case equality, checks both value and X/Z states)

– `!==` (Case inequality, checks both value and X/Z states)

4. Logical Operators

– Purpose: Perform logical operations, returning Boolean results.

– Examples:

– `&&` (Logical AND)

– `||` (Logical OR)

– `!` (Logical NOT)

5. Bitwise Operators

– Purpose: Perform bit-level operations.

– Examples:

– `&` (Bitwise AND)

– `|` (Bitwise OR)

– `^` (Bitwise XOR)

– `~` (Bitwise NOT)

6. Reduction Operators

– Purpose: Perform a bitwise reduction to a single bit.

– Examples:

– `&` (Reduction AND)

– `|` (Reduction OR)

– `^` (Reduction XOR)

– `~&` (Reduction NAND)

– `~|` (Reduction NOR)

– `~^` or `^~` (Reduction XNOR)

7. Shift Operators

– Purpose: Shift bits left or right.

– Examples:

– `<<` (Logical left shift)

– `>>` (Logical right shift)

– `<<<` (Arithmetic left shift)

– `>>>` (Arithmetic right shift)

8. Concatenation and Replication Operators

– Purpose: Combine multiple bits or replicate bits.

– Examples:

– `{}` (Concatenation)

– `{{}}` (Replication)

9. Conditional Operator

– Purpose: Perform a conditional operation (ternary operator).

– Example:

– `? :` (Condition ? True_Value : False_Value)

10. Assignment Operators

– Purpose: Assign values to variables or signals.

– Examples:

– `=` (Blocking assignment)

– `<=` (Non-blocking assignment)

11. Unary Operators

– Purpose: Operate on a single operand.

– Examples:

– `+` (Unary plus)

– `-` (Unary minus)

– `~` (Bitwise NOT)

12. Other Operators

– Purpose: Specialized operations.

– Examples:

– “ (Exponentiation in some Verilog extensions)

– `$` (System tasks/functions)

Understanding these operators is critical for designing and simulating hardware efficiently in Verilog.

COMMENTS