* Question

How Many Types of Load and Store Instructions Are Defined by Addressing Modes?

* Answer

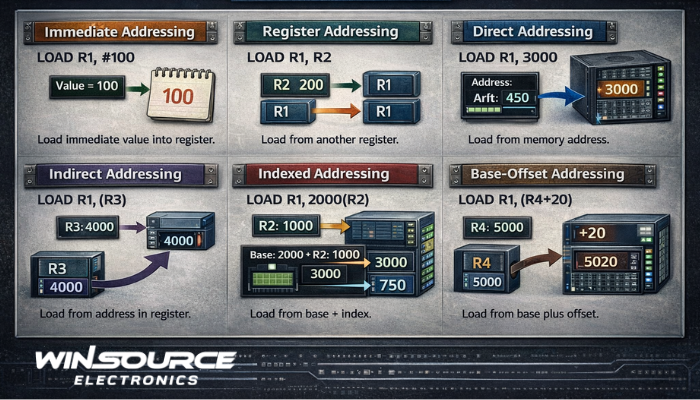

Load and store instructions are central to modern CPU architecture, especially in RISC-based processors where arithmetic operations cannot directly access memory. The diversity of load/store instructions largely depends on how the processor calculates the effective address of an operand.

From an address calculation perspective, load and store instructions can be classified into several core forms.

1. Direct (Absolute) Addressing

In direct addressing mode, the instruction contains the full memory address of the operand.

Effective Address = Address field inside the instruction

This method is straightforward but limited in flexibility. It is mostly found in early microprocessors or simple embedded systems with fixed memory layouts.

2. Register Indirect Addressing

Here, the instruction references a register that holds the memory address.

Effective Address = Contents of Register

Example:

LOAD R1, [R2]

This form is common in ARM, RISC-V, and MIPS architectures. It allows flexible memory access without increasing instruction length.

3. Base + Offset (Displacement Addressing)

This is the most widely used addressing mode in modern CPUs.

Effective Address = Base Register + Immediate Offset

Example:

LOAD R1, 16(R2)

It is heavily used for:

- Stack frame access

- Structure field access

- Local variable addressing

Most RISC architectures rely primarily on this addressing mechanism.

4. Indexed Addressing

Indexed addressing adds a second register for index calculation.

Effective Address = Base Register + Index Register

It is particularly efficient for array traversal and loop operations.

In some architectures, the index register may be automatically scaled depending on operand size.

5. Scaled Indexed Addressing (Base + Index × Scale + Offset)

Common in CISC architectures such as x86.

Effective Address = Base + (Index × Scale) + Offset

This form supports efficient high-level language constructs such as multi-dimensional arrays and complex data structures.

6. PC-Relative Addressing

Effective Address = Program Counter + Offset

This mode is widely used for:

- Branch instructions

- Position-independent code

- Embedded firmware

- Shared libraries

PC-relative addressing improves code relocation flexibility and security.

7. Auto-Increment / Auto-Decrement Addressing

Some architectures allow the address register to be automatically updated during the load/store operation.

Effective Address = Register (before or after update)

This is commonly used for:

- Stack operations

- Block memory transfer

- DMA buffer traversal

RISC vs. CISC: Why the Number Differs

RISC architectures typically implement fewer addressing modes to simplify pipeline design and improve instruction throughput.

CISC architectures offer more complex addressing forms to reduce instruction count and improve code density.

Therefore, the exact number of load/store instruction forms depends on the specific Instruction Set Architecture (ISA).

Engineering Insight

Understanding load/store addressing modes is essential for:

- Embedded system firmware optimization

- Compiler backend design

- Memory access performance tuning

- ISA comparison and processor selection

In high-performance or resource-constrained systems, memory access efficiency often determines overall execution behavior more than arithmetic throughput.

COMMENTS