* Question

How Does a Processor Enter an Exception Handling Routine?

* Answer

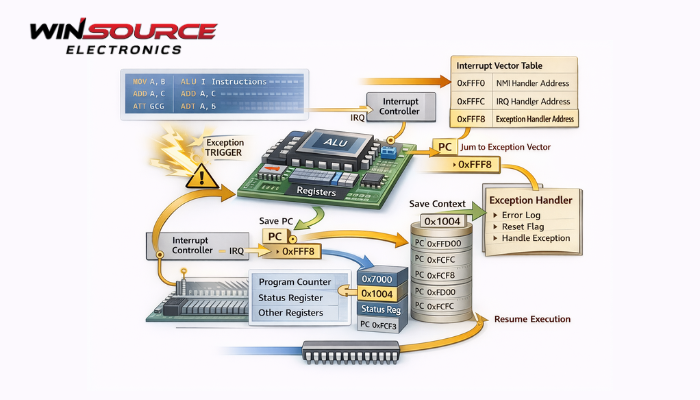

In microprocessors and microcontrollers, an exception execution program—often called an exception handler or interrupt service routine (ISR)—is a special piece of code that runs when the processor detects an abnormal condition or specific event. Exceptions can occur due to hardware faults, illegal instructions, memory access violations, or system interrupts.

To maintain system stability, the processor must temporarily suspend the current program and transfer control to a predefined exception handling routine. This transition follows a well-defined mechanism inside the CPU architecture.

1. Detection of an Exception Event

The first step occurs when the processor detects an exception condition. Exceptions may be generated by several sources, including:

- Hardware interrupts from external devices

- Internal faults such as divide-by-zero errors

- Invalid memory access or protection violations

- Illegal or undefined instructions

- System calls requested by software

When such an event occurs, the CPU’s exception control logic identifies the type of exception and initiates the exception handling process.

2. Suspension of the Current Program

Once the exception is recognized, the processor must preserve the state of the currently executing program so that it can resume later.

Typically, the processor automatically saves key information such as:

- Program Counter (PC)– the address of the next instruction

- Status Register or Flags– processor condition flags

- Sometimes general-purpose registers

These values are usually stored in a stack or dedicated system registers.

Saving the processor context ensures that the interrupted program can continue correctly after the exception handler finishes.

3. Locating the Exception Vector

After saving the processor state, the CPU determines where the exception handling routine is located. Most processor architectures use an exception vector table, which contains the addresses of different handlers.

Each exception type corresponds to a specific vector entry. For example:

- Reset vector

- External interrupt vector

- Divide-by-zero exception vector

- Page fault vector

The processor reads the appropriate vector entry and loads the handler address into the program counter.

4. Jumping to the Exception Handler

Once the handler address is obtained, the processor transfers control to the exception execution program.

At this stage:

- The CPU switches to the handler address

- Execution begins with the first instruction of the exception routine

- The handler analyzes the cause of the exception and performs the necessary operations

Typical tasks performed by exception handlers include:

- Clearing interrupt flags

- Handling hardware device requests

- Reporting system errors

- Recovering from faults

5. Returning from the Exception Routine

After the exception has been processed, the system must return to the interrupted program.

Most processors provide a special instruction such as:

- IRET (Interrupt Return)

- RETI (Return from Interrupt)

- ERET (Exception Return)

This instruction restores the previously saved processor state, including the program counter and status register. Execution then continues from the point where the exception occurred.

Conclusion

Entering an exception execution program is a structured process managed by the processor’s control logic. The sequence typically includes exception detection, program suspension, context saving, vector lookup, and transfer of control to the handler routine. After the handler completes its task, the processor restores the saved state and resumes normal execution.

This mechanism allows modern microcontrollers and processors to respond quickly to hardware events, system faults, and asynchronous interrupts, ensuring reliable operation in embedded and real-time systems.

COMMENTS