* Question

What are the main types of parallel statements in a VHDL architecture?

* Answer

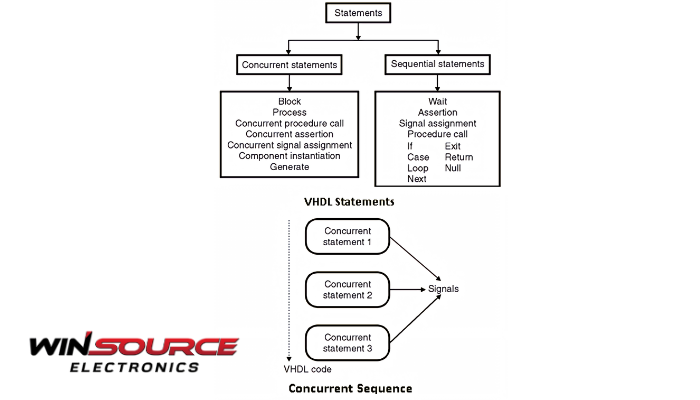

In VHDL, parallel statements define concurrent behavior within an architecture. The primary types of parallel statements include the following four categories:

1. Concurrent Signal Assignments

These are the simplest parallel constructs. Each assignment executes concurrently and is typically used to describe combinational logic.

Example:

a <= b AND c;

2. Conditional Signal Assignments

These assignments produce different signal outputs depending on specified conditions. They are often used to implement multiplexing behavior.

a <= b WHEN enable = ‘1’ ELSE c;

3. Selected Signal Assignments

Also known as selective signal assignments, this form selects an output value based on the value of a selector signal.

WITH sel SELECT

a <= b WHEN “00”,

c WHEN “01”,

d WHEN OTHERS;

4. Process Statements

A process is a concurrent block containing sequential statements. Processes run in parallel with each other but execute statements sequentially inside the block. They are widely used for describing both combinational and sequential logic.

process(clk)

begin

if rising_edge(clk) then

q <= d;

end if;

end process;

Summary

The main types of parallel statements in a VHDL architecture are:

- Concurrent Signal Assignments

- Conditional Signal Assignments

- Selected Signal Assignments

- Process Statements

These constructs collectively enable the modeling of concurrent hardware behavior in VHDL designs.

COMMENTS