* Question

What Are the Architectural Restrictions and Limitations of CPU Wait Mode?

* Answer

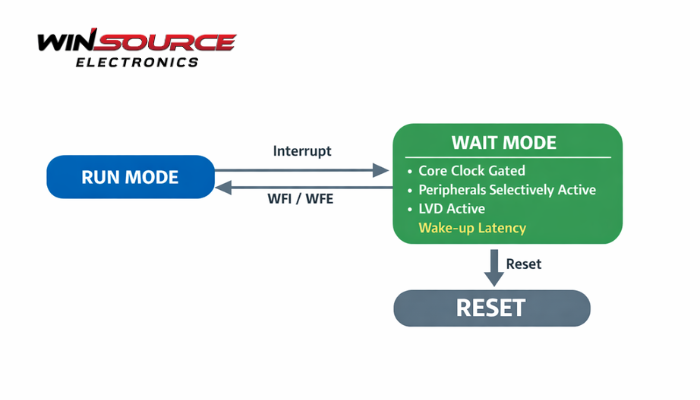

CPU wait mode (also referred to as sleep mode, standby mode, or WFI – Wait For Interrupt) is widely used in embedded systems and low-power processor architectures to reduce power consumption when no active tasks are running.

However, wait mode is not without architectural constraints. Its behavior depends heavily on clock gating design, interrupt structure, memory system configuration, and peripheral dependencies.

Below are the primary restrictions engineers must consider.

1. Execution Is Suspended — No Instruction Progress

When a processor enters wait mode:

- The instruction pipeline halts

- Program execution stops

- No arithmetic or memory operations are performed

The CPU can only resume execution upon a valid wake-up event, typically an interrupt or reset signal.

Restriction:

Wait mode cannot be used if background computation or polling is required.

2. Wake-Up Depends on Enabled Interrupt Sources

In most architectures (ARM Cortex-M, RISC-V, etc.), wait mode exits only when:

- A maskable interrupt occurs

- A non-maskable interrupt (NMI) occurs

- A reset event happens

If all interrupts are disabled or improperly configured, the CPU may remain indefinitely in wait mode.

Restriction:

Correct interrupt configuration is mandatory before entering wait mode.

3. Peripheral and Clock Dependencies

Many processors implement wait mode by:

- Gating the core clock

- Reducing system clock frequency

- Disabling selected peripheral clocks

If a peripheral required for wake-up is also clock-gated, the system may fail to resume properly.

Restriction:

Clock tree configuration must ensure wake-capable peripherals remain active.

4. Memory Access Constraints

In certain microcontroller architectures:

- Flash memory may enter low-power state

- SRAM retention may be partial

- External memory interfaces may be disabled

This creates limitations for systems requiring:

- Fast context restoration

- DMA-driven wake events

- External bus monitoring

Restriction:

Memory retention configuration determines data integrity during wait mode.

5. Latency Overhead on Resume

Although wait mode saves power, it introduces wake-up latency due to:

- Clock stabilization time

- PLL lock time

- Cache refill

- Pipeline restart

In real-time systems, this latency may violate timing constraints.

Restriction:

Wait mode is not suitable for ultra-low-latency real-time control loops.

6. Debugging Limitations

During wait mode:

- Debug interface access may be limited

- Breakpoints may not trigger

- Trace modules may pause

This can complicate system validation and firmware debugging.

Restriction:

Debug strategy must account for low-power states.

7. Not Equivalent to Deep Sleep or Power-Down Modes

Wait mode is typically lighter than deep sleep:

- CPU core stops

- But power domain remains active

It does not provide the same power savings as full power-down states.

Restriction:

Energy savings are moderate compared to deeper low-power modes.

Engineering Insight: When Should Wait Mode Be Used?

Wait mode is ideal for:

- Interrupt-driven embedded systems

- Event-based sensor nodes

- IoT devices

- Low-duty-cycle control systems

It is less suitable for:

- High-frequency real-time systems

- Continuous signal processing

- Systems requiring deterministic sub-microsecond response

Understanding the architectural limits of CPU wait mode allows engineers to balance power efficiency and system responsiveness more effectively.

COMMENTS