* Question

What Is the Difference Between Blocking and Non-Blocking Assignment in Verilog?

* Answer

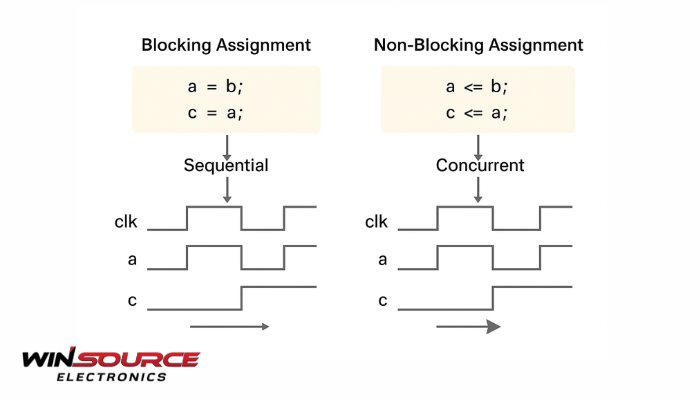

In Verilog HDL, assignments control how values are updated within simulation time and how data flows between registers and variables. Understanding the difference between blocking (=) and non-blocking (<=) assignments is essential for writing correct, predictable digital logic—especially in sequential circuits.

1. Blocking Assignment (=)

A blocking assignment executes in sequential order, meaning each statement must complete before the next one begins.

It behaves similarly to a normal programming language assignment (like in C or Python).

Syntax Example:

a = b;

c = a;

In this case:

a is first assigned the value of b.

Then c gets the (new) value of a.

The assignments “block” the execution of subsequent statements until they are done.

Use Case:

Typically used in combinational logic or testbenches, where operations occur sequentially and deterministically.

Best placed inside always @(*) blocks for modeling logic that doesn’t depend on clock edges.

2. Non-Blocking Assignment (<=)

A non-blocking assignment allows multiple assignments to occur concurrently within the same simulation time step.

It doesn’t block subsequent statements—updates are scheduled to occur at the end of the current time step.

Syntax Example:

a <= b;

c <= a;

Here:

Both assignments are evaluated at the same simulation time.

c receives the old value of a, not the updated one.

This mimics the parallel behavior of flip-flops in real hardware.

Use Case:

Used in sequential logic (e.g., clocked always blocks).

Ensures correct modeling of synchronous circuits where all registers update together at the clock edge.

3. Key Differences at a Glance

Aspect | Blocking Assignment (=) | Non-Blocking Assignment (<=) |

Execution Order | Sequential (one after another) | Concurrent (evaluated together) |

Behavior | Immediate update | Scheduled update (end of time step) |

Typical Usage | Combinational logic | Sequential/clocked logic |

Simulation Model | Procedural (software-like) | Hardware-like (register behavior) |

Risk | Can cause race conditions in sequential logic | Avoids timing races and mismatches |

4. Common Mistakes and Best Practices

Don’t mix = and <= assignments to the same variable within one always block—it leads to unpredictable simulation results.

Use blocking (=) in combinational always blocks (always @(*)).

Use non-blocking (<=) in clocked sequential blocks (always @(posedge clk)).

Keep style consistency for readability and hardware accuracy.

Summary

Blocking (=) assignments occur immediately and sequentially—ideal for modeling combinational logic.

Non-blocking (<=) assignments occur concurrently, mirroring synchronous flip-flop updates in hardware.

Mastering the difference ensures simulation accuracy, hardware consistency, and timing-correct RTL design—key factors in reliable digital system development.

COMMENTS