* Question

Which feedback modes does the Cyclone III PLL support?

* Answer

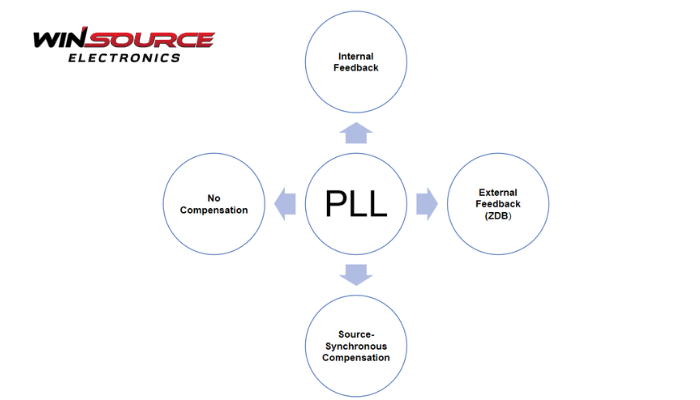

Cyclone III devices provide several PLL feedback/compensation modes to support different timing and clock-distribution scenarios. The main feedback modes are:

1. Internal Feedback Mode (Normal Mode)

- The PLL uses an internal feedback path.

- The output clock is phase-aligned with the reference clock inside the PLL.

- Simplest configuration; suitable for most general-purpose applications.

2. Zero-Delay Buffer (ZDB) / External Feedback Mode

- The feedback is taken externallyfrom a PLL output pin and routed back to the PLL’s feedback input.

- Eliminates clock tree delay so the output clock edge aligns with the input clock edge at the device boundary.

- Commonly used for driving external devices that require tight phase alignment.

3. Source-Synchronous Compensation Mode

- The PLL compensates for input or output delaysin source-synchronous interfaces.

- Used when capturing data using an incoming clock or forwarding a clock with data.

- Supports DDR, high-speed I/O, and other timing-critical interfaces.

4. No Compensation Mode

- The PLL does notperform delay compensation.

- Used for applications where only frequency synthesis is required, not phase alignment.

Summary

Cyclone III PLLs support the following feedback/compensation modes:

- Internal Feedback (Normal)

- External Feedback / Zero-Delay Buffer (ZDB)

- Source-Synchronous Compensation

- No Compensation

These modes allow designers to meet a wide range of timing, synchronization, and interface requirements in FPGA-based systems.

COMMENTS