* Question

What Are the Challenges of Stacked Silicon Interconnect Technology?

* Answer

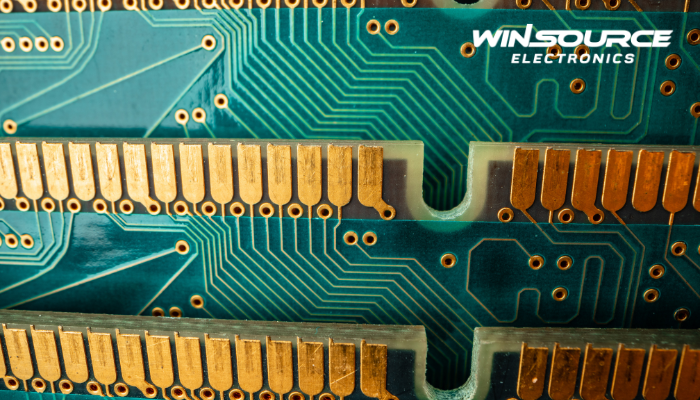

Stacked Silicon Interconnect (SSI) technology, which involves vertically stacking multiple layers of silicon chips and interconnecting them using advanced techniques, offers significant benefits in terms of space-saving, performance, and power efficiency. However, there are several challenges that must be addressed for SSI technology to be fully optimized. Below are some of the key problems associated with SSI technology:

1. Thermal Management

- Challenge: One of the primary concerns with SSI is heat dissipation. Since multiple layers of chips are stacked together, managing the heat generated by each layer becomes more difficult. The heat accumulation within the stacked layers can lead to overheating, negatively impacting performance and potentially damaging components.

- Solution: Effective thermal management solutions are required, such as advanced cooling systems, thermal vias, and materials with better heat conductivity. Designers also need to consider the thermal characteristics of the stacked layers and ensure sufficient heat dissipation.

2. Manufacturing Complexity

- Challenge: The process of stacking multiple silicon layers and connecting them with precise interconnects is highly complex and requires advanced fabrication techniques. The alignment of layers during the stacking process must be extremely precise to ensure reliable interconnects. Any misalignment or defects can lead to faulty connections and unreliable performance.

- Solution: Advances in wafer bonding, microbumps, and through-silicon vias (TSVs)have helped reduce these challenges, but they still require high-precision manufacturing processes and quality control to ensure successful stacking.

3. Interconnect Resistance and Signal Integrity

- Challenge: As more layers are stacked, the complexity and resistance of the interconnects increase. This can lead to signal integrity issues, such as delays, crosstalk, and signal degradation, especially at high frequencies. The quality of the interconnects between the layers is crucial to maintain the system’s performance.

- Solution: Advanced interconnect materialsand design techniques are needed to minimize resistance and ensure signal integrity. Innovations such as low-resistance TSVs and fine-pitch interconnects are being explored to overcome these challenges.

4. Power Consumption

- Challenge: Power distribution across stacked silicon layers can be problematic, as ensuring consistent power delivery to each layer becomes more difficult. Additionally, power consumption tends to increase as more layers are added, leading to potential thermal and efficiency concerns.

- Solution: Power management techniques such as power gating, dynamic voltage and frequency scaling (DVFS), and on-chip voltage regulationare used to address these challenges and reduce power consumption.

5. Cost

- Challenge: The manufacturing of stacked silicon interconnects involves complex and expensive processes, such as wafer thinning, bonding, and TSV fabrication. The increased cost of these processes can make SSI technology more expensive than traditional 2D packaging, which could hinder its widespread adoption.

- Solution: As SSI technology matures, economies of scale and improvements in manufacturing techniques are expected to reduce the costs. However, the price remains a significant consideration for large-scale deployment, especially for cost-sensitive applications.

6. Reliability and Testing

- Challenge: Testing stacked silicon interconnects is more challenging than traditional single-layer devices. The increased complexity of stacked layers requires new methods to test the integrity and functionality of each layer and its interconnections. Additionally, the reliability of stacked structures over time must be validated to avoid potential failure due to mechanical stress or thermal cycling.

- Solution: Enhanced non-destructive testingmethods, such as X-ray inspection and advanced electrical testing techniques, are being developed to ensure the reliability and quality of stacked silicon devices. Continuous improvements in design and materials also help increase the overall reliability.

Conclusion

While stacked silicon interconnect technology offers many advantages, including increased performance, reduced footprint, and lower power consumption, it faces challenges related to thermal management, manufacturing complexity, interconnect resistance, power consumption, cost, and reliability. By addressing these issues through innovations in materials, manufacturing processes, and design techniques, SSI technology can continue to evolve and become more widely adopted for a range of advanced electronic applications.

COMMENTS