* Question

What are the commonly used operators for VHDL?

* Answer

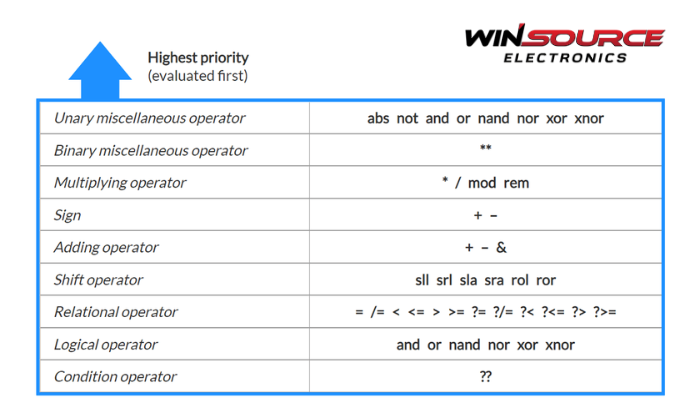

In VHDL (VHSIC Hardware Description Language), operators are used to perform various operations on data types such as bit, boolean, std_logic, integer, and others. They are categorized into several types based on functionality.

Below is a detailed classification of the commonly used VHDL operators:

Table of Contents

Toggle1. Logical Operators

Used for boolean and std_logic types.

Operator | Description | Usage Example |

and | Logical AND | A and B |

or | Logical OR | A or B |

nand | Logical NAND | A nand B |

nor | Logical NOR | A nor B |

xor | Logical XOR | A xor B |

xnor | Logical XNOR | A xnor B |

not | Logical NOT | not A |

Note: These are often used with signals of type std_logic, boolean, or bit.

2. Relational Operators

Used for comparing two values; return a boolean result.

Operator | Description | Usage Example |

= | Equal to | A = B |

/= | Not equal to | A /= B |

< | Less than | A < B |

<= | Less than or equal | A <= B |

> | Greater than | A > B |

>= | Greater or equal | A >= B |

3. Arithmetic Operators

Used for numeric types such as integer, real, or vector types (signed, unsigned from IEEE libraries).

Operator | Description | Usage Example |

+ | Addition | A + B |

– | Subtraction | A – B |

* | Multiplication | A * B |

/ | Division | A / B |

mod | Modulo | A mod B |

rem | Remainder | A rem B |

** | Exponentiation | A ** B (only for real or integer) |

4. Shift and Rotation Operators (defined in IEEE 1076-2008 or numeric_std)

Operator | Description | Usage Example |

sll | Shift left logical | A sll 2 |

srl | Shift right logical | A srl 3 |

sla | Shift left arithmetic | A sla 1 |

sra | Shift right arithmetic | A sra 2 |

rol | Rotate left | A rol 1 |

ror | Rotate right | A ror 1 |

5. Concatenation Operator

Used to join vectors or bits.

Operator | Description | Usage Example |

& | Concatenation | “01” & “10” → “0110” |

6. Miscellaneous

Unary Minus / Plus: -A, +A

Aggregate assignment: (others => ‘0’) is often used for initializing vectors.

Type Conversion Functions (not operators, but commonly used):

to_integer(), to_unsigned(), to_signed() from numeric_std.

Notes:

Many arithmetic and logical operations on std_logic_vector require type conversion to signed or unsigned when using numeric_std.

VHDL is strongly typed. Operator overloading (via packages like numeric_std) enables operations on composite types.

Conclusion:

VHDL offers a wide range of operators for logic, arithmetic, and data manipulation tasks in digital design. Choosing the correct operator, along with proper type handling, is crucial to ensure synthesis-friendly and simulation-accurate HDL code.

COMMENTS