* Question

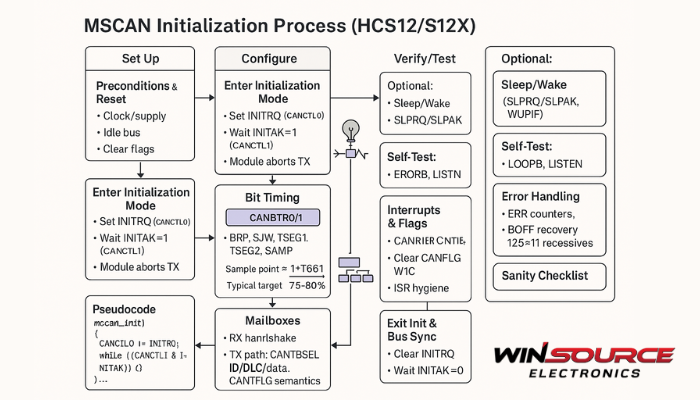

What is included in the MSCAN initialization process?

* Answer

Table of Contents

Toggle0) Preconditions & reset

Clock & supply stable; CAN transceiver powered.

Bus state: recessive (idle) on CANH/CANL; no stuck-dominant faults.

After reset: clear pending flags in CANRFLG (write-1-to-clear).

1) Enter Initialization Mode

Request init: set INITRQ in CANCTL0.

Wait acknowledge: poll INITAK in CANCTL1 = 1.

Notes: in init mode the module aborts any TX, leaves bus sync, filters are idle.

2) Module & clock options (CANCTL1)

Clock source: set CLKSRC (bus clock vs. external oscillator, depends on MCU).

Self-test / bring-up:

LOOPB = 1 → internal loopback (no transceiver required).

LISTEN = 1 → listen-only (receives but never drives the bus).

Optional: enable time-stamp or prescaler options if your variant supports them.

3) Bit-timing configuration (CANBTR0 / CANBTR1)

Program fields:

BRP (clock prescaler / time-quantum), SJW (sync jump width),

TSEG1, TSEG2 (phase segments), SAMP (1- or 3-sample).

Design method (portable):

Pick TQ count per bit: NTQ=1+TSEG1+TSEG2. Common choices: 8–16 TQ.

Aim sample point ≈1+TSEG1/NTQ = 75–80 % (e.g., TSEG1=7, TSEG2=2 → 80%).

Compute prescaler from the device’s TQ formula (datasheet specific). Generic pattern:

Bitrate=fclk/(scale)×(BRP+1)×NTQ

where scale may be 1 or 2 depending on MCU. Solve for BRP and round to valid range.

Choose SJW ≤ TSEG2 (often 1–2 TQ).

If noise is high or bus long, consider SAMP=1 (single) with generous TSEG1, or SAMP=1 plus careful filtering; use SAMP=1 unless the reference manual advises 3-sample.

Verify with oscilloscope (CANH/CANL) or by receiving frames in LISTEN mode.

4) Acceptance filtering (CANIDAC + CANIDARx/CANIDMRx)

Filter scheme (in CANIDAC): choose 2×32-bit, 4×16-bit, or 8×8-bit to balance ID granularity vs. number of filters.

Program acceptance (CANIDARx) and mask (CANIDMRx) bytes for standard (11-bit) or extended (29-bit) IDs.

Mask semantics (important): mask bit = 1 → “don’t care”, mask bit = 0 → “compare”.

Tip: keep a small mapping diagram (ID bit → register bit) in comments to avoid off-by-one errors.

5) Message buffers / mailboxes

Receive: ensure the RX buffer is empty before enabling interrupts; reading the RX frame registers then clearing RXF in CANRFLG (W1C) completes the handshake.

Transmit:

Select a TX buffer with CANTBSEL, write ID/DLC/data registers for that buffer.

Request transmission by clearing the corresponding bit in CANTFLG (on MSCAN, a ‘0’ in CANTFLG means “busy/requested”; check your variant).

Optionally set priority if supported; poll CANTFLG or enable CANTIER to get an interrupt when the buffer becomes empty again.

6) Interrupts & flags

Enable required sources in CANRIER (RX full, overrun, wake-up, error, bus-off) and CANTIER (TX).

Clear any pending flags in CANRFLG before exiting init (write 1 to clear). Typical bits: RXF, OVRIF, WUPIF, ERRIF, BOFF.

ISR hygiene: in RX ISR, copy the frame out, then clear RXF (W1C). In TX ISR, service the buffer and rely on CANTFLG to know which TX mailbox triggered.

7) Exit Initialization & bus synchronization

Exit: clear INITRQ (CANCTL0); wait until INITAK (CANCTL1) = 0.

Synchronize: before transmitting, ensure the controller is bus-synchronized (after seeing at least one edge / 11 recessive bits per CAN spec). A simple practice is to receive one valid frame in LISTEN mode, then enable TX.

8) Sleep / low-power / wake-up (optional but common)

Enter sleep: set SLPRQ (CANCTL0); wait SLPAK (CANCTL1) = 1.

Wake-up: enable wake-up interrupt (CANRIER), clear WUPIF prior, then leave sleep by clearing SLPRQ or on bus activity (implementation-dependent).

Order: always clear flags (W1C) before enabling their interrupts to avoid false triggers.

9) Self-test & bring-up shortcuts

LOOPB = 1: transmit and receive internally; validate bit timing & mailboxes without a transceiver.

LISTEN = 1: monitor a live bus passively to confirm your bit rate and filters before you ever drive the line.

10) Errors & bus-off handling

Error counters / state: track RX/TX error counters (device-specific registers) and state (Error Active/Passive).

Bus-off: when BOFF is set, the node must not transmit. Recovery per CAN spec after 128 occurrences of 11 recessive bits; some systems prefer a software-controlled re-init (set INITRQ, clear flags, re-enter normal).

Overrun: if OVRIF asserts, increase ISR budget or lower RX load; always clear with W1C and consider enabling a second filter/buffer if available.

11) Minimal initialization skeleton (C-style pseudocode)

void mscan_init(uint32_t f_clk, uint32_t bitrate) {

/* 1. Enter init */

CANCTL0 |= INITRQ;

while (!(CANCTL1 & INITAK)) {}

/* 2. Clock & modes */

// CANCTL1 = (CANCTL1 & ~CLKSRC_MASK) | CLKSRC_BUSCLK;

// Optionally: LOOPB=0, LISTEN=0 for normal

/* 3. Bit timing (example fields; compute for your f_clk/bitrate) */

// CANBTR0 = (SJW<<6) | BRP;

// CANBTR1 = (SAMP<<7) | (TSEG2<<4) | TSEG1;

/* 4. Acceptance filters */

// CANIDAC = MODE_4x16; // pick a scheme

// CANIDAR0.. = <acceptance bytes>; // IDs you accept

// CANIDMR0.. = <mask bytes>; // 1=don’t care, 0=compare

/* 5. Clear flags, enable interrupts */

CANRFLG = 0xFF; // W1C typical

// CANRIER = RXFIE | OVRIE | ERRIE | BOFFIE; // as needed

// CANTIER = TXEIE; // if TX interrupts

/* 6. Exit init */

CANCTL0 &= ~INITRQ;

while (CANCTL1 & INITAK) {}

/* 7. Optional: wait for sync or first valid frame before TX */

}

12) Quick acceptance filter example (standard ID)

Goal: receive only ID = 0x123.

Approach: write 0x123 into acceptance registers; set mask bits 0 for those ID bits (must match), 1 for all others (don’t care).

To accept a range (e.g., 0x120–0x12F), set mask 1 on the low 4 bits.

13) Sanity checklist

INITRQ/INITAK handshakes OK; flags cleared with W1C.

Bit-rate math → expected sample point ~80 %; scope looks clean.

Filters accept only intended IDs; TX mailbox handshake understood.

LISTEN/LOOPB tests pass; normal mode frames TX/RX; error and bus-off paths verified.

With these additions—sleep/wake, sync criteria, bit-timing method, filter semantics, mailbox use, interrupts, and bus-off—you have an initialization section that’s still concise but deployment-ready for real MSCAN designs.

COMMENTS