* Question

Which stage of the 3-stage pipeline instruction is executed?

* Answer

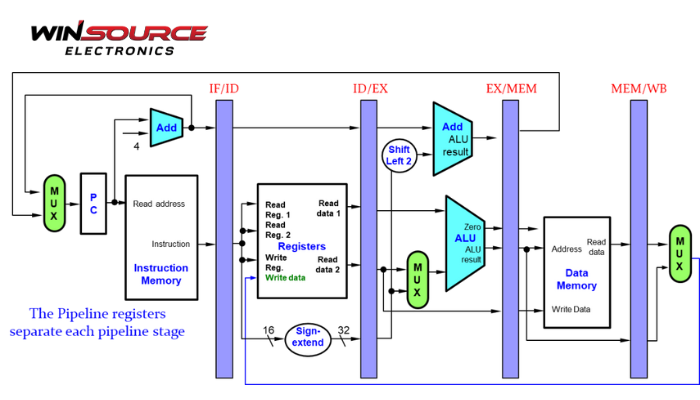

In a 3-stage pipeline architecture, the instruction is typically executed in three distinct stages. These stages are usually divided as follows:

Table of Contents

Toggle1. Fetch (IF) – Instruction Fetch:

In this stage, the instruction is fetched from memory (usually the instruction cache) based on the program counter (PC).

The instruction is retrieved from memory and is passed to the next stage for decoding.

2. Decode (ID) – Instruction Decode:

In this stage, the fetched instruction is decoded. The control unit identifies the type of instruction and determines the operands needed for execution.

The registers (if used by the instruction) are read during this stage, and the operands are prepared for execution in the next stage.

The program counter (PC) may be updated if the instruction requires branching or control flow change.

3. Execute (EX) – Execution:

In this stage, the actual operation specified by the instruction is executed. For example, arithmetic or logical operations are performed by the Arithmetic Logic Unit (ALU), or memory addresses are calculated for load/store instructions.

In the case of a branch instruction, this is the stage where the branch target address is calculated and the branch decision is made.

The results of the execution are passed to the next pipeline stage (in a more complex pipeline, this could be a memory access or write-back stage).

In a 3-stage pipeline, the Execute (EX) stage is the stage where the actual instruction execution occurs. This is the phase where arithmetic or logic operations are performed, and the results are typically written to registers or memory, depending on the instruction type.

After the Execute stage, depending on the pipeline’s design, there may be additional stages for memory access or result writing (e.g., a memory access stage or write-back stage in more complex pipelines), but in a simple 3-stage pipeline, execution happens in the third stage.

COMMENTS